# 400G ZR+ QSFP-DD Coherent Optical Module FVL-400T75C40CY

#### Features

- Operating rate up to 478.75 Gbps

- PM-QPSK (200G) and PM-16QAM (200G / 400G) modulation formats

- 400GE, 200GE and OTU4 / OTUCn services

- Hot-pluggable QSFP-DD form factor

- 8 × CEI-56G-VSR electrical interfaces

- QSFP-DD-Hardware-rev6p3 compliant

- QSFP-DD-CMIS-rev5p2 compliant

- Lock registers

- Maximum power consumption: 24 W

#### Applications

The module is designed for ZR 400G DCI / PTN applications and ZR+200G metro long-haul OTN applications. It provides high-speed data channels, IIC interface module control and state alarm reporting with 3.3 V power supplied.

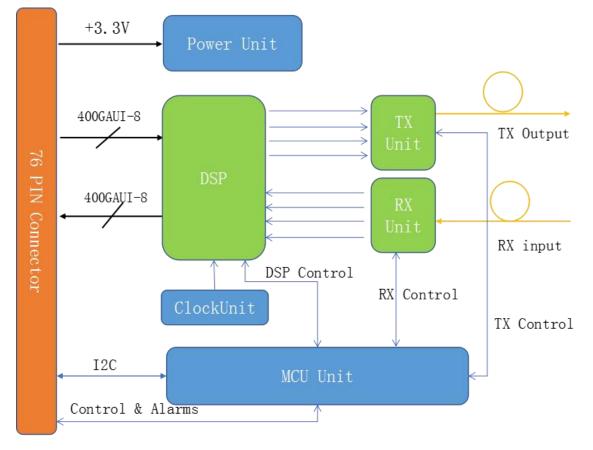

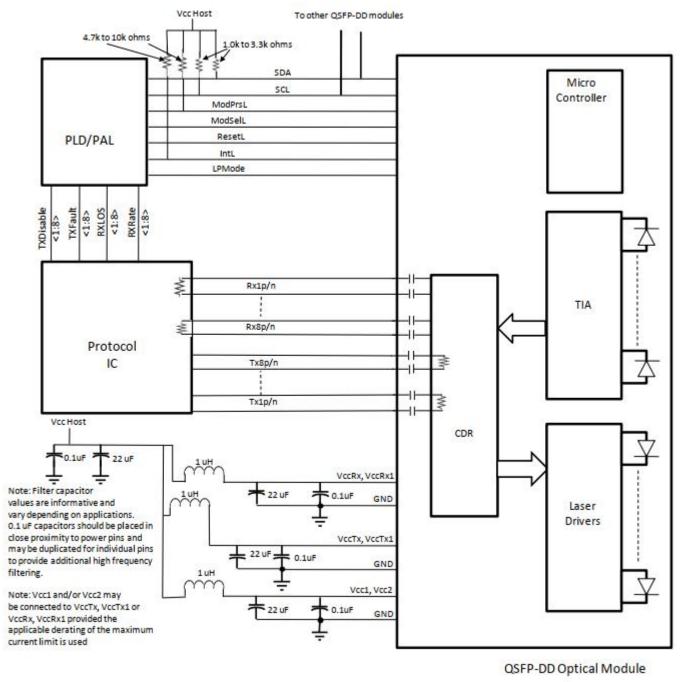

#### General

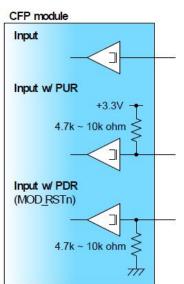

The QSFP-DD coherent optical module uses a 76-pin connector as an electrical interface to connect the system board. The module comprises TX unit, RX unit and control units. All control interface pins work properly with the help of the internal MCU which itself can also be used for modulator control, software management, alarm performance reporting and other functions.

Figure 1 Module Block Diagram

#### **Module Characteristics**

200G Optical Port

### Table 1 200G Optical Port Performance Specifications

| Parameter                       | Value                                   |

|---------------------------------|-----------------------------------------|

| Network lane, modulation format | PM-QPSK                                 |

| Optical channels                | 80                                      |

| Grid spacing                    | 75 GHz                                  |

| Frequency range                 | 190.7 to 196.65 THz                     |

| Wavelength stability            | ±1.5 GHz                                |

| Tx output power, default        | -0.5 dBm                                |

| Max. Tx output power            | -0.5 dBm                                |

| Min. Tx output power            | -6 dBm                                  |

| Tx output power accuracy        | ±1.5 dB                                 |

| Output power during tuning      | < -35 dBm                               |

| CD tolerance                    | ±40 000 ps/nm                           |

| DGD tolerance                   | 33 ps                                   |

| Input power range               | 0 to -18 dBm                            |

| OSNR tolerance (BOL)            | 15 dB (Rx optical power: -8 to -10 dBm) |

| Power consumption               | Typical: 22 W<br>Maximum: 24 W          |

| Parameter                       | Value                                     |

|---------------------------------|-------------------------------------------|

| Network lane, modulation format | PM-16QAM                                  |

| Optical channels                | 96                                        |

| Grid spacing                    | 50 GHz                                    |

| Frequency range                 | 191.3 to 196.05 THz                       |

| Wavelength stability            | ±1.5 GHz                                  |

| Tx output power, default        | -0.5 dBm                                  |

| Max. Tx output power            | -0.5 dBm                                  |

| Min. Tx output power            | -6 dBm                                    |

| Tx output power accuracy        | ±1.5 dBm                                  |

| Output power during tuning      | < -35 dBm                                 |

| CD tolerance                    | ±10 000 ps/nm                             |

| DGD tolerance                   | 22 ps                                     |

| Input power range               | 0 to -18 dBm                              |

| OSNR tolerance (BOL)            | 19.5 dB (Rx optical power: -8 to -10 dBm) |

| Power consumption               | Typical: 18 W<br>Maximum: 20 W            |

#### **400G Optical Port**

#### Table 2 400G Optical Port Performance Specifications

| Parameter                       | Value                                   |

|---------------------------------|-----------------------------------------|

| Network lane, modulation format | PM-16QAM (ZR+)                          |

| Optical channels                | 80                                      |

| Grid spacing                    | 75 GHz                                  |

| Frequency range                 | 190.7 to 196.65 THz                     |

| Wavelength stability            | ±1.5 GHz                                |

| Tx output power, default        | -0.5 dBm                                |

| Max. Tx output power            | -0.5 dBm                                |

| Min. Tx output power            | -6 dBm                                  |

| Tx output power accuracy        | ±1.5 dBm                                |

| Output power during tuning      | < -35 dBm                               |

| CD tolerance                    | ±9 000 ps/nm                            |

| DGD tolerance                   | 22 ps                                   |

| Input power range               | 0 to -10 dBm                            |

| OSNR tolerance (BOL)            | 24 dB (Rx optical power: -8 to -10 dBm) |

| Power consumption               | Typical: 22 W<br>Maximum: 24 W          |

#### **Electrical Characteristics**

#### **Power Supply Requirements**

The QSFP-DD coherent optical module has six designated pins on the 76-pin connector for its own power feed. The host board supplies a stable power to the module which in turn limits the inrush charging current of the hot-swappable devices. Power feed to all internal devices in the optical module is converted from the host board through the connector. Table 3 describes the power supply requirements. All voltages are tested at the connector interface.

## FIBERSTAMP

#### Table 3 QSFP-DD Coherent Optical Module Power Supply Requirements

| Parameter                                                                                                                                                                                                            | Symbol                         | Min                                     | Nom              | Max         | Unit   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------|------------------|-------------|--------|

| Power supply voltages VccTx, VccTx1,                                                                                                                                                                                 |                                | 3.135                                   | 3.3              | 3.465       | V      |

| VecRx, VecRx1, Vecl & Vec2 including                                                                                                                                                                                 |                                | 8300 S.S.S.S.                           | -30264           | -91/1-9-783 | 12     |

| ripple, droop and noise below 100kHz1                                                                                                                                                                                |                                |                                         |                  |             | -      |

| Host RMS noise output 40 Hz-10 MHz                                                                                                                                                                                   |                                |                                         |                  | 25          | mV     |

| Module RMS noise output 10 Hz - 10 MHz                                                                                                                                                                               |                                |                                         | 8 - 8            | 30          | mV     |

| Module power supply noise tolerance 10 Hz                                                                                                                                                                            | PSNRmod                        | 1                                       | 8 - St           | 66          | mV     |

| - 10 MHz (peak-to-peak)<br>Module inrush - instantaneous peak                                                                                                                                                        | T_ip                           |                                         |                  | 50          | μs     |

| duration <sup>2</sup><br>Module inrush - initialization time <sup>2</sup>                                                                                                                                            | T. init                        | - 0                                     | G 3              | 500         |        |

|                                                                                                                                                                                                                      | T_init<br>Power Mode           | 107                                     | 21. K            | 500         | ms     |

| Power Consumption                                                                                                                                                                                                    | P 1p                           |                                         | 0 0              | 1.5         | W      |

| Instantaneous peak current at hot plug                                                                                                                                                                               | Icc ip lp                      | -                                       | -                | 600         | mA     |

| Sustained peak current at hot plug                                                                                                                                                                                   | Icc sp lp                      |                                         | <u> </u>         | 495         | mA     |

| Steady state current                                                                                                                                                                                                 | Icc lp                         | 6,538#                                  | See Not          | 55,57       | mA     |

| High Power Mode                                                                                                                                                                                                      |                                |                                         | See Not          | ve o        | , ilia |

| Power Consumption                                                                                                                                                                                                    | P 1                            | 1 module                                | 10 10            | 1.5         | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc ip 1                       | -                                       | 0 2 0            | 600         | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc sp 1                       |                                         |                  | 495         | mA     |

|                                                                                                                                                                                                                      |                                | 1 2070                                  | Con Mar          |             |        |

| Steady state current                                                                                                                                                                                                 | Icc_1                          |                                         | See Not          | ce 3        | mA     |

| High Power Mode                                                                                                                                                                                                      |                                | 2 module                                | 14               |             |        |

| Power Consumption                                                                                                                                                                                                    | P_2                            |                                         | 10 N             | 3.5         | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc_ip_2                       | -                                       |                  | 1400        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc_sp_2                       | -                                       | -                | 1155        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc_2                          |                                         | See Not          | te 3        | mA     |

| High Power Mode                                                                                                                                                                                                      |                                | 3 module                                | 10 01            |             |        |

| Power Consumption                                                                                                                                                                                                    | P_3                            |                                         | 6 8              | 7           | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc_ip_3                       | -                                       | -                | 2800        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc_sp_3                       | 10750                                   | 1 5 1            | 2310        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc_3                          | 1 To | See Not          | te 3        | mA     |

| High Power Mode                                                                                                                                                                                                      |                                | 4 module                                |                  |             |        |

| Power Consumption                                                                                                                                                                                                    | P_4                            |                                         | 1 N              | 8           | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc_ip_4                       | · · · · ·                               |                  | 3200        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc_sp_4                       |                                         | -                | 2640        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc_4                          |                                         | See Not          | te 3        | mA     |

| High Power Mode                                                                                                                                                                                                      | Power Class                    | 5 module                                | (6) (3)          | ž           | 5      |

| Power Consumption                                                                                                                                                                                                    | P_5                            |                                         |                  | 10          | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc_ip_5                       | 100                                     |                  | 4000        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc_sp_5                       | 828                                     | 8 4 8            | 3300        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc 5                          | 1                                       | See Not          | te 3        | mA     |

| High Power Mode                                                                                                                                                                                                      | Power Class                    | 6 module                                |                  |             | ×3.    |

| Power Consumption                                                                                                                                                                                                    | P 6                            | 1                                       | 8                | 12          | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc_ip_6                       | -                                       | - <del></del>    | 4800        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc sp 6                       | 1                                       |                  | 3960        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc 6                          | 1                                       | See Not          |             | mA     |

| High Power Mode                                                                                                                                                                                                      |                                |                                         |                  |             |        |

| Power Consumption                                                                                                                                                                                                    | P 7                            | 1                                       | 1                | 14          | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc ip 7                       | 1020                                    | 5 4 3            | 5600        | mA     |

| Sustained peak current                                                                                                                                                                                               | Icc sp 7                       | 100                                     | 2                | 4620        | mA     |

| Steady state current                                                                                                                                                                                                 | Icc 7                          | 8                                       | See Not          |             | mA     |

| High Power Mode                                                                                                                                                                                                      |                                |                                         |                  |             |        |

| Power Consumption                                                                                                                                                                                                    | P 84                           |                                         |                  | >14         | W      |

| Instantaneous peak current                                                                                                                                                                                           | Icc ip 8                       |                                         |                  | P 8/2.5     | A      |

| Sustained peak current                                                                                                                                                                                               | Icc sp 8                       |                                         | 2 2 3            | P 8/3.03    | A      |

| Steady state current                                                                                                                                                                                                 |                                | 10020                                   | 2                | <u></u> 6   | A      |

|                                                                                                                                                                                                                      | Icc_8                          | 10                                      | 8 <sup>–</sup> 8 | 0           | A      |

| Note 1: Measured at VccTx, VccTx1, VccRx,<br>Note 2: T_ip and T_init are test condition<br>characteristics of the module<br>Note 3: The module must stay within its de<br>Note 4: User must read management register | s for measuri:<br>clared power | ng inrush<br>class.                     |                  |             |        |

The QSFP-DD coherent optical module provides multiple electrical interfaces. For details, see Table 4.

#### Table 4 QSFP-DD Coherent Optical Module

| Client Type | Interface Type | Electrical Standards                  |

|-------------|----------------|---------------------------------------|

| 100GE       | CAUI-4         | IEEE 802.3bm CAUI-4<br>Chip-to-Module |

| 100GE       | 100GAUI-2      | IEEE 802.3bm GAUI-8<br>Chip-to-Module |

| Client Type                      | Interface Type     | Electrical Standards                  |

|----------------------------------|--------------------|---------------------------------------|

| 200GE                            | 200GAUI-8          | OIF CEI-28G VSR                       |

| 200GE                            | 200GAUI-4          | IEEE 802.3bm GAUI-8<br>Chip-to-Module |

| 400GE                            | 400GAUI-8          |                                       |

| OTU4                             | OTL4.4             | OIF CEI-28G VSR                       |

| OTU4                             | OTL4.2             | OIF CEI-56G VSR PAM-4                 |

| OTUC1 / OTUC2                    | FOIC1.4 (FlexO-SR) | OIF CEI-28G VSR                       |

| OTUC1 / OTUC2<br>/ OTUC3 / OTUC4 | FOIC1.2 (FlexO-SR) | OIF CEI-56G VSR PAM-4                 |

| OTUC4                            | FOIC4.8 (FlexO-SR) | OIF CEI-56G VSR PAM-4                 |

#### **REFCLK (Reference Clock)**

The QSFP-DD coherent optical module does not require the host board to provide a reference clock (REFCLK).

#### TXMCLK (Transmitter Monitor Clock)

The Tx side of the QSFP-DD coherent optical module does not provide a monitor clock (TXMCLK) for monitoring Tx optical signals.

#### **Control Pins (non-IIC) Functional Description**

#### ModSelL (Module Selection)

Module selection (ModSelL) is an input pin which is pulled up to Vcc in the module. When ModSelL is driven low by the host, the module responds to serial communication commands from the IIC bus. The ModSelL allows the use of multiple QSFP-DD modules at one IIC interface bus. When ModSelL is driven high by the host, the module does not respond to any command from the IIC interface. To avoid conflicts, after deselecting all QSFP-DD modules, the host should not attempt to communicate through the IIC interface during the ModSelL failure time. Similarly, the host should wait at least one ModSelL effective cycle before communicating with the newly selected QSFP-DD module. For details about ModSelL Setup Time (tSU.ModSelL) and ModSelL Hold Time (tHD.ModSelL), see Table 8.

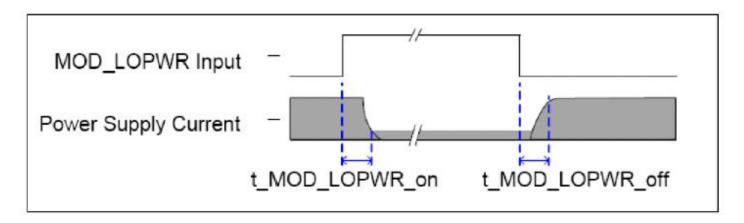

#### MOD\_LOPWR (Module Low Power)

MOD\_LOPWR is a signal input pin from the host and works in the logic high state. When MOD\_LOPWR is logic high, the optical module works at low power consumption and remains in this mode. When MOD\_LOPWR is pulled low, the optical module is initialized to a high power consumption mode, that is, the normal operation mode. In low power consumption mode, the optical module communicates through the MDIO management interface, and its maximum power consumption does not

exceed 2 W. Refer to Table 8 for the timing diagram of MOD\_LOPWR. For values of "t\_MOD\_LOPWR\_on" and "t\_ MOD\_LOPWR\_off", see Figure 4.

Figure 4 Timing Diagram for MOD\_LOPWR

#### ResetL (Module Reset)

ResetL is a signal input pin which is pulled up to Vcc in the module. The QSFP-DD module is completely reset when ResetL is driven by a low level signal with a pulse length longer than the minimum pulse length (t\_Reset\_init). After reset, all user settings of the module are restored to their default states.

#### Alarm Pins (non-MDIO) Functional Description

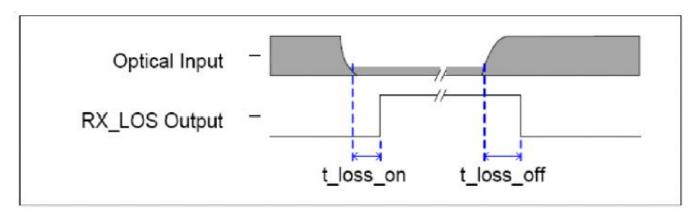

#### RX\_LOS (Receiver Loss of Signal)

RX\_LOS is a signal output pin which transmits signals to the host board and works at the logic high state. When RX\_LOS is logic high, the optical power received by the optical module is too low. Figure 5 shows the timing diagram for RX\_LOS.

Figure 5 Timing Diagram for RX\_LOS

#### MOD\_ABS (Module Absent)

MOD\_ABS is a signal output pin which transmits signals from the inside of the module to the host board. This pin is pulled up on the host board but pulled down to the ground inside the module. When the optical module is inserted into the host board, MOD\_ABS is logic low, meaning that the module is present. When no optical module is on the host board, MOD\_ABS is logic high, meaning that the module is absent.

#### **Control and Alarm Descriptions**

#### Timing Parameters for Control and Alarm Signals

| Parameter               | Symbol      | Min. | Тур. | Max.  | Unit                  | Notes                     |

|-------------------------|-------------|------|------|-------|-----------------------|---------------------------|

| Transmitter Disabled    | t_off       |      |      | 100   |                       | Application specific.     |

| (TX_DIS high)           |             |      |      | 100   | μs                    | Defined by module vendor. |

| Transmitter Enabled     | ton         |      |      | 25    |                       | Application specific.     |

| (TX_DIS low)            | t_on        |      |      | 25    | S                     | Defined by module vendor. |

|                         | t_MOD_LOPWR |      |      | 0.5   |                       | Application specific.     |

| MOD_LOPWR assert        | _assert     |      |      | 9.5   | S                     | Defined by module vendor. |

|                         | t_MOD_LOPWR |      | 10   |       | Application specific. |                           |

| MOD_LOPWR deassert      | _deassert   | 0.1  |      | 10    | S                     | Defined by module vendor. |

| Receiver Loss of Signal |             | 0.5  |      | 100   |                       | Application specific.     |

| Assert Time             | t_loss_on   | 0.5  |      | 400   | μs                    | Defined by module vendor. |

| Receiver Loss of        |             | 0.5  |      | 100   |                       | Application specific.     |

| Signal De-assert Time   | t_loss_off  | 0.5  |      | 400 µ | μs                    | Defined by module vendor. |

| Management              | tprd        | 250  |      |       | ns                    | MDC is 4 MHz rate         |

#### Table 6 Signal Timing Parameters

| Parameter              | Symbol       | Min. | Тур. | Max. | Unit | Notes |

|------------------------|--------------|------|------|------|------|-------|

| Interface Clock Period |              |      |      |      |      |       |

| Host MDIO setup        | tsetup       | 4    |      |      | ns   |       |

| time                   |              |      |      |      |      |       |

| Host MDIO hold time    | thold        | 3.2  |      |      | ns   |       |

| Module MDIO delay      | tdelay       | 0    |      | 175  | ns   |       |

| time                   |              | 0    |      | 175  | 113  |       |

| Initialization time    | t_initialize | 19   |      | 120  | S    |       |

| from Reset             |              |      |      | 120  | 3    |       |

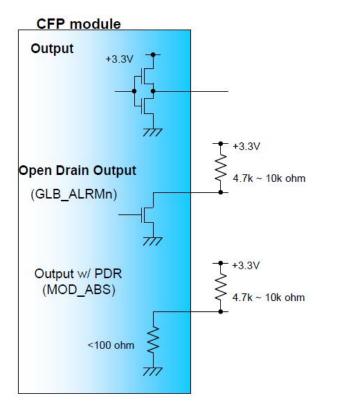

#### Control and Alarm Pins: 3.3V LVCMOS Electrical Characteristics

The hardware control and alarm pins specified as 3.3V LVCMOS functionality described above shall meet the electrical characteristics described in Table 7. Their reference input and output termination modes are shown in Figure 6.

Table 7 3.3V LVCMOS Electrical Characteristics

| Parameter                                          | Symbol | Min.    | Тур. | Max.    | Unit |

|----------------------------------------------------|--------|---------|------|---------|------|

| Power supply voltage                               | VCC    | 3.2     | 3.3  | 3.4     | V    |

| Input high voltage                                 | VIH    | 2       |      | VCC+0.3 | V    |

| Input low voltage                                  | VIL    | -0.3    |      | 0.8     | V    |

| Input leakage current                              | IIN    | -10     |      | 10      | μA   |

| Output high voltage<br>(I <sub>OH</sub> = -100 µA) | VOH    | VCC-0.2 |      |         | V    |

| Output low voltage<br>(I <sub>OL</sub> = 100 µA)   | VOL    |         |      | 0.2     | V    |

#### Figure 2-6: Reference +3.3V LVCMOS Output

Termination

#### Figure 2-7: Reference +3.3V LVCMOS Input

Figure 6 Reference 3.3V LVCMOS Input / Output Termination

#### Module Management Interface (IIC) Description

#### Management Data Input / Output Interface (IIC)

The QSFP-DD module uses IIC to communicate with related cores on host ASICs. As a hot-swappable interface, the IIC interface supports bus topologies.

#### Management Data Clock Pins (SCL)

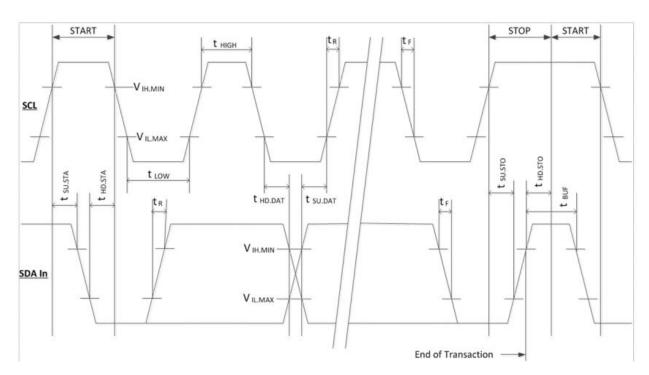

The host defines a default clock rate of up to 400 KHz for the IIC, optionally supporting up to 1 MHz. Figure 7 shows the timing diagram for SCL and SDA pins and Table 8 describes their specific timing parameters. This section strictly conforms to the QSFP SFF-8636 specifications.

Figure 7 Timing Diagram for the SCL & SDA Pins

|                                                                         |                    |     | Mode | Fast |         |            |                                                                                                                              |

|-------------------------------------------------------------------------|--------------------|-----|------|------|---------|------------|------------------------------------------------------------------------------------------------------------------------------|

|                                                                         |                    |     | kHz) |      | (1 MHz) |            |                                                                                                                              |

| Parameter                                                               | Symbol             | Min | Max  | Min  | Max     | Unit       | Conditions                                                                                                                   |

| Clock Frequency                                                         | fSCL               | 0   | 400  | 0    | 1000    | kHz        |                                                                                                                              |

| Clock Pulse Width<br>Low                                                | tLOW               | 1.3 |      | 0.50 |         | μs         |                                                                                                                              |

| Clock Pulse Width<br>High                                               | tHIGH              | 0.6 |      | 0.26 |         | μs         |                                                                                                                              |

| Time bus free<br>before new<br>transmission can<br>start                | tBUF               | 20  |      | 1    |         | μs         | Between STOP and START and between ACK and ReStart                                                                           |

| START Hold Time                                                         | tHD.STA            | 0.6 |      | 0.26 |         | μs         | The delay required between SDA<br>becoming low and SCL starting<br>to go low in a START                                      |

| START Setup Time                                                        | tSU.STA            | 0.6 |      | 0.26 |         | μs         | The delay required between SCL<br>becoming high and SDA starting<br>to go low in a START                                     |

| Data In Hold Time                                                       | tHD.DAT            | 0   |      | 0    |         | μs         | Burit's and a second second                                                                                                  |

| Data In Setup Time                                                      | tSU.DAT            | 0.1 |      | 0.1  |         | μs         |                                                                                                                              |

| Input Rise Time                                                         | tR                 |     | 300  |      | 120     | ns         | From (VIL,MAX=0.3*Vcc) to<br>(VIH, MIN=0.7*Vcc)                                                                              |

| Input Fall Time                                                         | tF                 |     | 300  |      | 120     | ns         | From (VIH, MIN=0.7*Vcc) to<br>(VIL, MAX=0.3*Vcc)                                                                             |

| STOP Setup Time                                                         | tSU.STO            | 0.6 | Č.   | 0.26 |         | μs         |                                                                                                                              |

| STOP Hold Time                                                          | tHD.STO            | 0.6 | 1    | 0.26 |         | μs         |                                                                                                                              |

| Aborted sequence -<br>bus release                                       | Deselect<br>_Abort |     | 2    |      | 2       | ms         | Delay from a host de-asserting<br>ModSelL (at any point in a bus<br>sequence) to the QSFP-DD<br>module releasing SCL and SDA |

| ModSelL Setup Time <sup>1</sup>                                         | tSU.<br>ModSelL    | 2   |      | 2    |         | ms         | ModSelL Setup Time is the<br>setup time on the select line<br>before the start of a host<br>initiated serial bus sequence.   |

| ModSelL Hold Time <sup>1</sup>                                          | tHD.<br>ModSelL    | 2   |      | 2    |         | ms         | ModSelL Hold Time is the delay<br>from completion of a serial bu<br>sequence to changes of module<br>select status.          |

| Serial Interface<br>Clock Holdoff<br>"Clock Stretching"                 | T_clock_<br>hold   |     | 500  |      | 500     | us         | Maximum time the QSFP-DD<br>module may hold the SCL line<br>low before continuing with a<br>read or write operation          |

| Complete Single<br>or Sequential<br>Write to non-<br>volatile registers | tWR                |     | 80   |      | 80      | ms         | Complete Write of up to 8<br>Bytes                                                                                           |

| Accept a single or<br>sequential write<br>to volatile<br>memory.        | tNACK              |     | 80   |      | 80      | ms         | Time required for the module<br>to accept a single or<br>sequential write to volatile<br>memory.                             |

| Endurance (Write<br>Cvcles)                                             |                    | 50K |      |      | 50k     | cycl<br>es |                                                                                                                              |

#### Table 8 IIC Interface Timing Parameters

#### IIC Physical Interface Address Pin (ModSelL)

The serial port address of the IIC interface is 1010000X (A0h). To access to multiple QSFP-DD modules on one IIC serial bus, each QSFP-DD's 76-pin connector provides a module selection pin (ModSeIL). ModSeIL is pulled high by default, meaning the corresponding module is not selected. If it is pulled low by the host, this module is selected and can communicate with the host through the IIC interface.

#### IIC Interface Pins: Vcc-based LVCMOS Electrical Characteristics

The IIC pins working in Vcc-based LVCMOS mode described above shall meet the electrical characteristics described in Table 9. Their reference input and output termination modes are shown in Figure 9.

| Parameter                                    | Symbol        | Min.    | Max.    | Unit                                                           | Condition                                                                                 |

|----------------------------------------------|---------------|---------|---------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| SCL and SDA                                  | VOL           | 0       | 0.4     | V                                                              | IOL(max)=3 mA for fast mode, 20<br>mA for Fast-mode plus                                  |

|                                              | VIL           | -0.3    | Vcc*0.3 | V                                                              |                                                                                           |

| SCL and SDA                                  | VIH           | Vcc*0.7 | Vcc+0.5 | V                                                              |                                                                                           |

| Capacitance for SCL<br>and SDA I/O signal    | Ci            |         | 14      | pF                                                             |                                                                                           |

| Total bus capacitive<br>load for SCL and SDA | СЬ            |         | 100     | pF                                                             | For 400 kHz clock rate use 3.0 k<br>Ohms Pullup resistor, max. For<br>1000 kHz clock rate |

| IDdd IOFSCE and SDA                          | nd SDA 200 pF |         | pF      | For 400 kHz clock rate use 1.6 k<br>Ohms pullup resistor, max. |                                                                                           |

| LPMode, ResetL,                              | VIL           | -0.3    | 0.8     | V                                                              |                                                                                           |

| ModSelL and Epps                             | VIH           | 2       | VCC+0.3 | V                                                              |                                                                                           |

| LPMode, ResetL and<br>ModSelL                | lin           |         | 360     | μΑ                                                             | 0V <vin<vcc< td=""></vin<vcc<>                                                            |

#### Table 9 Vcc-based LVCMOS Electrical Characteristics

### FIBERSTAMP

Figure 9 IIC Interface Reference Termination Mode

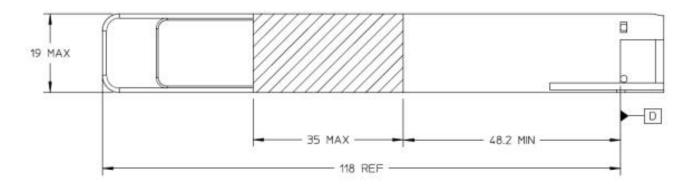

#### **Mechanical Dimensions**

Figure 9 shows mechanical dimensions of the QSFP-DD coherent optical module.

Max. dimensions (L × W × H): 93.3 mm × 18.35 mm × 8.5 mm.

Figure 9 Mechanical Dimensions of the QSFP-DD Optical Module

#### **Operating Environment**

#### **Table 9 Operating Environment**

| Parameter                                                          | Min. | Max.                                     | Unit | Notes |

|--------------------------------------------------------------------|------|------------------------------------------|------|-------|

| Storage temperature                                                | -40  | 85                                       | °C   |       |

| Operating case temperature                                         | 0    | 70                                       | °C   |       |

| Relative humidity, operating (non-condensing)                      | 5    | 85                                       | %    |       |

| Relative humidity, operating (short term < 96 hrs, non-condensing) | 5    | 95                                       | %    |       |

| ESD sensitivity (HBM)                                              |      | High-speed pins: 500<br>Other pins: 2000 | V    |       |

#### Pin Assignment and Description

Electrical connections of 76 pins include eight pairs of TX differential signals (input TXIs of the module, connecting to signal outputs of the card), eight pairs of RX differential signals (output RXOs of the module, connecting to signal inputs of the card), control pins, alarm pins, IIC communication related pins, GND pins, +3.3V power supply pins and some reserved pins.

| Pad | Logic                                    | Symbol  | Description                         | Plug<br>Sequence <sup>4</sup> | Notes |

|-----|------------------------------------------|---------|-------------------------------------|-------------------------------|-------|

| 1   |                                          | GND     | Ground                              | 1B                            | 1     |

| 2   | CML-I                                    | Tx2n    | Transmitter Inverted Data Input     | 3B                            | 1     |

| 3   | CML-I                                    | Tx2p    | Transmitter Non-Inverted Data Input | 3B                            | 200   |

| 4   |                                          | GND     | Ground                              | 1B                            | 1     |

| 5   | CML-I                                    | Tx4n    | Transmitter Inverted Data Input     | 3B                            |       |

| 6   | CML-I                                    | Tx4p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 7   | -2. K. M. C. C.                          | GND     | Ground                              | 1B                            | 1     |

| 8   | LVTTL-I                                  | ModSelL | Module Select                       | 3B                            |       |

| 9   | LVTTL-I                                  | ResetL  | Module Reset                        | 3B                            |       |

| 10  |                                          | VccRx   | +3.3V Power Supply Receiver         | 2B                            | 2     |

| 11  | LVCMOS-<br>I/O                           | SCL     | 2-wire serial interface clock       | 3B                            | 8     |

| 12  | LVCMOS-<br>I/O                           | SDA     | 2-wire serial interface data        | 3B                            |       |

| 13  |                                          | GND     | Ground                              | 1B                            | 1     |

| 14  | CML-O                                    | Rx3p    | Receiver Non-Inverted Data Output   | 3B                            |       |

| 15  | CML-O                                    | Rx3n    | Receiver Inverted Data Output       | 3B                            |       |

| 16  |                                          | GND     | Ground                              | 1B                            | 1     |

| 17  | CML-O                                    | Rxlp    | Receiver Non-Inverted Data Output   | 3B                            | 1     |

| 18  | CML-O                                    | Rxln    | Receiver Inverted Data Output       | 3B                            |       |

| 19  |                                          | GND     | Ground                              | 1B                            | 1     |

| 20  |                                          | GND     | Ground                              | 1B                            | 1     |

| 21  | CML-O                                    | Rx2n    | Receiver Inverted Data Output       | 3B                            |       |

| 22  | CML-O                                    | Rx2p    | Receiver Non-Inverted Data Output   | 3B                            |       |

| 23  | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. | GND     | Ground                              | 18                            | 1     |

| 24  | CML-O                                    | Rx4n    | Receiver Inverted Data Output       | 3B                            |       |

| 25  | CML-O                                    | Rx4p    | Receiver Non-Inverted Data Output   | 3B                            | -     |

| 26  |                                          | GND     | Ground                              | 18                            | 1     |

| 27  | LVTTL-O                                  | ModPrsL | Module Present                      | 3B                            |       |

| 28  | LVTTL-O                                  | IntL    | Interrupt                           | 3B                            | -     |

| 29  |                                          | VCCTX   | +3.3V Power supply transmitter      | 2B                            | 2     |

| 30  |                                          | Vccl    | +3.3V Power supply                  | 2B                            | 2     |

| 31  | LVTTL-I                                  | LPMode  | Low Power mode;                     | 3B                            | -     |

| 32  |                                          | GND     | Ground                              | 1B                            | 1     |

| 33  | CML-I                                    | Tx3p    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 34  | CML-I                                    | Tx3n    | Transmitter Inverted Data Input     | 3B                            | 25    |

| 35  |                                          | GND     | Ground                              | 1B                            | 1     |

| 36  | CML-I                                    | Txlp    | Transmitter Non-Inverted Data Input | 3B                            |       |

| 37  | CML-I                                    | Txln    | Transmitter Inverted Data Input     | 3B                            | S     |

| 38  |                                          | GND     | Ground                              | 1B                            | 1     |

| Pad | Logic        | Symbol   | Description                                            | Plug<br>Sequence <sup>4</sup> | Notes |

|-----|--------------|----------|--------------------------------------------------------|-------------------------------|-------|

| 39  |              | GND      | Ground                                                 | 1A                            | 1     |

| 40  | CML-I        | Tx6n     | Transmitter Inverted Data Input                        | 3A                            | -     |

| 41  | CML-I        | Тхбр     | Transmitter Non-Inverted Data Input                    | 3A                            | ŝ     |

| 42  |              | GND      | Ground                                                 | 1A                            | 1     |

| 43  | CML-I        | Tx8n     | Transmitter Inverted Data Input                        | 3A                            | Sec.C |

| 44  | CML-I        | Tx8p     | Transmitter Non-Inverted Data Input                    | 3A                            | 8     |

| 45  |              | GND      | Ground                                                 | 1A                            | 1     |

| 46  | 2            | Reserved | For future use                                         | 3A                            | 3     |

| 47  | 1 (j         | VS1      | Module Vendor Specific 1                               | 3A                            | 3     |

| 48  |              | VccRx1   | 3.3V Power Supply                                      | 2A                            | 2     |

| 49  | 2            | VS2      | Module Vendor Specific 2                               | 3A                            | 3     |

| 50  | i            | VS3      | Module Vendor Specific 3                               | ЗA                            | 3     |

| 51  |              | GND      | Ground                                                 | 1A                            | 1     |

| 52  | CML-O        | Rx7p     | Receiver Non-Inverted Data Output                      | 3A.                           |       |

| 53  | CML-O        | Rx7n     | Receiver Inverted Data Output                          | 3A                            | 2     |

| 54  |              | GND      | Ground                                                 | 1A                            | 1     |

| 55  | CML-O        | Rx5p     | Receiver Non-Inverted Data Output                      | 3A.                           |       |

| 56  | CML-0        | Rx5n     | Receiver Inverted Data Output                          | 3A                            | ġ.    |

| 57  |              | GND      | Ground                                                 | 1A                            | 1     |

| 58  | E 101 10 - 3 | GND      | Ground                                                 | 1A                            | 1     |

| 59  | CML-O        | Rx6n     | Receiver Inverted Data Output                          | ЗA                            |       |

| 60  | CML-O        | Rx6p     | Receiver Non-Inverted Data Output                      | 3A                            |       |

| 61  | i            | GND      | Ground                                                 | 1A                            | 1     |

| 62  | CML-O        | Rx8n     | Receiver Inverted Data Output                          | 3A                            |       |

| 63  | CML-O        | Rx8p     | Receiver Non-Inverted Data Output                      | 3A                            | 1     |

| 64  |              | GND      | Ground                                                 | 1A                            | 1     |

| 65  |              | NC       | No Connect                                             | 3A                            | 3     |

| 66  |              | Reserved | For future use                                         | 3A                            | 3     |

| 67  | i            | VccTx1   | 3.3V Power Supply                                      | 2A                            | 2     |

| 68  |              | Vcc2     | 3.3V Power Supply                                      | 2A                            | 2     |

| 69  | LVTTL-I      | ePPS     | Precision Time Protocol (PTP) reference<br>clock input | 3A                            | 3     |

| 70  |              | GND      | Ground                                                 | 1A                            | 1     |

| 71  | CML-I        | Tx7p     | Transmitter Non-Inverted Data Input                    | 3A                            |       |

| 72  | CML-I        | Tx7n     | Transmitter Inverted Data Input                        | 3A.                           | 2     |

| 73  |              | GND      | Ground                                                 | 1A                            | 1     |

| 74  | CML-I        | Tx5p     | Transmitter Non-Inverted Data Input                    | 3A                            |       |

| 75  | CML-I        | Tx5n     | Transmitter Inverted Data Input                        | 3A                            | 2     |

| 76  |              | GND      | Ground                                                 | 1A                            | 1     |

Note 1: QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

Note 2: VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 7. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins are each rated for a maximum current of 1000 mA.

Note 3: All Vendor Specific, Reserved, No Connect and ePPS (if not used) pins may be terminated with 50 Ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF. Note 4: Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A,1B will then occur simultaneously, followed by 2A,2B,followed by 3A,3B.

#### **Reliability Specifications**

#### Laser Safety

The module design conforms to Class 1 laser requirements and complies with IEC / EN 60825 - 1 / A2: 2001 and FDA CDRH21 cfr - 1040. When the module is working, do not look directly at an optical port at any time.

#### **ESD Sensitivity**

According to the GR-78 standard (Human Body Model using C =100pF, R = 1.5k Ohm), the module design provides ESD sensitivity (HBM) of 500 V for high-speed pins and 2000 V for other pins in anti-static workplaces.

#### **Electromagnetic Radiation**

According to the GR-1089-CORE standard, the module design meets Class B requirements.

#### **RoHS** Compliance

The module meets the requirements of the RoHS Directive 2010/571/EU.

#### Model

| Model           | Description                               |

|-----------------|-------------------------------------------|

| FVL-400T75C40CY | 400G QSFP-DD Coherent Optical Module, ZR+ |