# 400GbE QSFP56-DD to 2x200G QSFP56 Breakout Active Optical Cable

# FYL2H-400MxxxC

#### **Features**

- Hot-plug QSFP56-DD and QSFP56 form factor

- 8x 50Gb/s PAM4 modulation

- Supports NRZ 200G aggregate bit rates if requiredNote1

- Low power dissipation <9W (400G End)</li>

- Low power dissipation <5W (200G End)</li>

- RoHS-6 compliant (lead-free)

- Commercial case temperature range of 0°C to 70°C

- Single 3.3V power supply

- Maximum link length of 70m on OM3 MMF

- and 100m on OM4 & OM5 MMF

- Uncooled 850nm VCSEL array (both End)

- PIN photo detector array (both End)

- 400GBASE-SR8 and 200GBASE-SR4 compliant

- I2C management interface

- CMIS V4.0 compliant

#### **Applications**

IEEE 802.3cd 200GBASE-SR4 Ethernet (PAM4)

#### **Description**

FIBERSTAMP's FYL2H-400MxxxC MMF Active Optical Splitter Cable is used in 2 X 200 Gigabit Ethernet links over OM3/OM4/OM5 multimode fiber, which provides connectivity between system units with a 400GbE connector on one side and two separate 200GbE connectors on the other two sides. The cable connects data signals from each of the 8 MMF (Multi Mode Fiber) pairs on the single QSFP56-DD end to the dual pair of each of the QSFP56 multiport ends.

FIBERSTAMP's GDA2-MD0401-XXXCA MMF Active Optical Splitter Cable is compliant with the QSFP-DD-MSA and with 200GBASE-SR4 specification. Digital diagnostics functions are available via the I2C interface as specified by CMIS V4.0. The transceiver is RoHS 2.0 compliant and lead-free per Directive 2011/65/EU.

#### Note:

1. Contact FIBERSTAMP for more details.

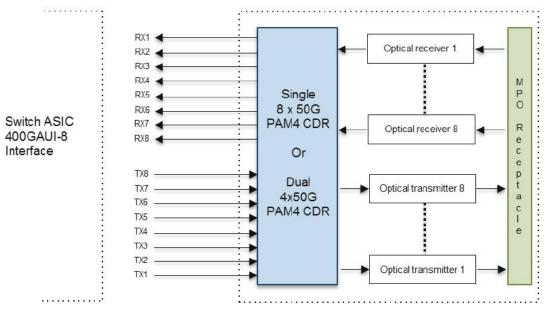

Figure 1. Module Block Diagram (400G End)

#### **Absolute Maximum Ratings**

| A Laborator Markings       |                 |      |                      |      |  |  |

|----------------------------|-----------------|------|----------------------|------|--|--|

| Parameter                  | Symbol          | Min  | Max                  | Unit |  |  |

| Supply Voltage             | V <sub>cc</sub> | -0.3 | 3.6                  | V    |  |  |

| Input Voltage              | V <sub>in</sub> | -0.3 | V <sub>cc</sub> +0.3 | V    |  |  |

| Storage Temperature        | Ts              | -20  | 85                   | °C   |  |  |

| Case Operating Temperature | T <sub>c</sub>  | 0    | 70                   | °C   |  |  |

| Humidity (non-condensing)  | Rh              | 5    | 95                   | %    |  |  |

# **Recommended Operating Conditions**

| Parameter                  | Symbol          | Min  | Typical | Max  | Unit    |

|----------------------------|-----------------|------|---------|------|---------|

| Supply Voltage             | V <sub>cc</sub> | 3.13 | 3.3     | 3.47 | ٧       |

| Operating Case Temperature | Tc              | 0    |         | 70   | °C      |

| Baud Rate per Lane (PAM4)  | fd              |      | 26.5625 |      | GBaud/s |

| Humidity                   | Rh              | 5    |         | 85   | %       |

| Power Dissipation          | P <sub>m</sub>  |      |         | 9.0  | W       |

| Fiber Bend Radius          | Rb              | 3    |         |      | cm      |

### **Electrical Specifications**

| incented openications                                 |                  |                      |         |                 |       |  |  |

|-------------------------------------------------------|------------------|----------------------|---------|-----------------|-------|--|--|

| Parameter                                             | Symbol           | Min                  | Typical | Max             | Unit  |  |  |

| Differential Input Impedance                          | Z <sub>in</sub>  | 90                   | 100     | 110             | ohm   |  |  |

| Differential Output Impedance                         | Z <sub>out</sub> | 90                   | 100     | 110             | ohm   |  |  |

| Differential Input Voltage Amplitude <sup>Note2</sup> | $\Delta V_{in}$  | 300                  |         | 900             | mVppd |  |  |

| Differential Output Voltage Amplitude                 | $\Delta V_{out}$ | 300                  |         | 900             | mVppd |  |  |

| Bit Error Rate Note3                                  | BER              |                      |         | 2.4E-4          |       |  |  |

| Input Logic Level High                                | V <sub>IH</sub>  | 2.0                  |         | V <sub>cc</sub> | ٧     |  |  |

| Input Logic Level Low                                 | V <sub>IL</sub>  | 0                    |         | 0.8             | ٧     |  |  |

| Output Logic Level High                               | V <sub>ОН</sub>  | V <sub>cc</sub> -0.5 |         | V <sub>cc</sub> | ٧     |  |  |

| Output Logic Level Low                                | V <sub>OL</sub>  | 0                    |         | 0.4             | V     |  |  |

#### Note:

- 1. Suggested < 700mVpp input differential signal for better BER performance.

- 2. Pre-FEC BER, compliant with IEEE802.3cd 200GBASE-SR4 specification.

# **Optical Characteristics**

| Parameter                                                         | Symbol             | Min  | Typical | Max | Unit |

|-------------------------------------------------------------------|--------------------|------|---------|-----|------|

| Transmitter                                                       |                    |      |         |     |      |

| Center Wavelength                                                 | λс                 | 840  | 850     | 860 | nm   |

| RMS Spectral Width                                                | Δλ                 |      |         | 0.6 | nm   |

| Average Launch Power (each lane)                                  | P <sub>out</sub>   | -6   |         | 6   | dBm  |

| Outer Optical Modulation Amplitude (each lane)                    | OMA <sub>out</sub> | -4   |         | 5   | dBm  |

| Launch power in OMA <sub>outer</sub> minus TDECQ                  | P <sub>tdecq</sub> | -5.9 |         |     | dBm  |

| Transmitter and dispersion eye closure (each lane)                | TDECQ              |      |         | 4.9 | dB   |

| Average launch power of off transmitter(each lane)                | P <sub>off</sub>   |      |         | -30 | dBm  |

| Outer Extinction Ratio                                            | ER                 | 3    |         |     | dB   |

| Optical Return Loss Tolerance                                     | ORLT               |      |         | 12  | dB   |

| R                                                                 | eceiver            |      |         |     |      |

| Center Wavelength                                                 | λ <sub>c</sub>     | 840  | 850     | 860 | nm   |

| Damage threshold                                                  | Rdam               | 6    |         |     | dBm  |

| Average Receive Power (each lane) Input (each lane)               | Pin                | -7.9 |         | 4   | dBm  |

| Receiver Power (OMA <sub>outer</sub> ) (each lane)                | OMA <sub>out</sub> |      |         | 3   | dBm  |

| Receiver reflectance                                              | Pref               |      |         | -12 | dB   |

| Stressed Receiver Sensitivity (OMA <sub>outer</sub> ) (each lane) | Sens               |      |         | -3  | dBm  |

| Receiver Sensitivity (OMA <sub>outer</sub> ) (each lane) Note4    | Sen                |      |         | -7  | dB   |

#### Note:

1. Measured with conformance test signal at TP3 for the BER specified in section 138.1.1 of IEEE 802.3cd.

# **Pin Description**

| Pin | Logic   | Symbol  | Name/Description                    |

|-----|---------|---------|-------------------------------------|

| 1   |         | GND     | Module Ground <sup>Note5</sup>      |

| 2   | CML-I   | Tx2-    | Transmitter inverted data input     |

| 3   | CML-I   | Tx2+    | Transmitter non-inverted data input |

| 4   |         | GND     | Module Ground Note5                 |

| 5   | CML-I   | Tx4-    | Transmitter inverted data input     |

| 6   | CML-I   | Tx4+    | Transmitter non-inverted data input |

| 7   |         | GND     | Module Ground <sup>Note5</sup>      |

| 8   | LVTTL-I | MODSEIL | Module Select <sup>Note6</sup>      |

| 9   | LVTTL-I | ResetL  | Module Reset <sup>Note6</sup>       |

# FIBERSTAMP

| Pin | Logic      | Symbol  | Name/Description                                                 |  |

|-----|------------|---------|------------------------------------------------------------------|--|

| 10  |            | VCCRx   | +3.3V Power Supply                                               |  |

| 11  | LVCMOS-I   | SCL     | 2-wire Serial interface clock <sup>Note6</sup>                   |  |

| 12  | LVCMOS-I/O | SDA     | 2-wire Serial interface data <sup>Note6</sup>                    |  |

| 13  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 14  | CML-O      | RX3+    | Receiver non-inverted data output                                |  |

| 15  | CML-O      | RX3-    | Receiver inverted data output                                    |  |

| 16  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 17  | CML-O      | RX1+    | Receiver non-inverted data output                                |  |

| 18  | CML-O      | RX1-    | Receiver inverted data output                                    |  |

| 19  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 20  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 21  | CML-O      | RX2-    | Receiver inverted data output                                    |  |

| 22  | CML-O      | RX2+    | Receiver non-inverted data output                                |  |

| 23  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 24  | CML-O      | RX4-    | Receiver inverted data output                                    |  |

| 25  | CML-O      | RX4+    | Receiver non-inverted data output                                |  |

| 26  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 27  | LVπl-O     | ModPrsL | Module Present, internal pulled down to GND                      |  |

| 28  | LVπl-O     | IntL    | Interrupt output, should be pulled up on host board <sup>2</sup> |  |

| 29  |            | VCCTx   | +3.3V Transmitter Power Supply                                   |  |

| 30  |            | VCC1    | +3.3V Power Supply                                               |  |

| 31  | LVTTL-I    | LPMode  | Low Power Mode <sup>Note6</sup>                                  |  |

| 32  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 33  | CML-I      | Tx3+    | Transmitter non-inverted data input                              |  |

| 34  | CML-I      | Tx3-    | Transmitter inverted data input                                  |  |

| 35  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 36  | CML-I      | Tx1+    | Transmitter non-inverted data input                              |  |

| 37  | CML-I      | Tx1-    | Transmitter inverted data input                                  |  |

| 38  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 39  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| 40  | CML-I      | Tx6-    | Transmitter inverted data input                                  |  |

| 41  | CML-I      | Tx6+    | Transmitter non-inverted data input                              |  |

| 42  |            | GND     | Module Ground Note5                                              |  |

| 43  | CML-I      | Tx8-    | Transmitter inverted data input                                  |  |

| 44  | CML-I      | Tx8+    | Transmitter non-inverted data input                              |  |

| 45  |            | GND     | Module Ground <sup>Note5</sup>                                   |  |

| Pin | Logic | Symbol | Name/Description                    |

|-----|-------|--------|-------------------------------------|

| 46  |       |        |                                     |

| 47  |       | TBD    | For future use                      |

| 48  |       | VCC    | +3.3V Receiver Power Supply         |

| 49  |       | TBD    | For future use                      |

| 50  |       | TBD    | For future use                      |

| 51  |       | GND    | Module Ground <sup>Note5</sup>      |

| 52  | CML-O | RX7+   | Receiver non-inverted data output   |

| 53  | CML-O | RX7-   | Receiver inverted data output       |

| 54  |       | GND    | Module Ground <sup>Note5</sup>      |

| 55  | CML-O | RX5+   | Receiver non-inverted data output   |

| 56  | CML-O | RX5-   | Receiver inverted data output       |

| 57  |       | GND    | Module Ground <sup>Note5</sup>      |

| 58  |       | GND    | Module Ground <sup>Note5</sup>      |

| 59  | CML-O | RX6-   | Receiver inverted data output       |

| 60  | CML-O | RX6+   | Receiver non-inverted data output   |

| 61  |       | GND    | Module Ground <sup>Note5</sup>      |

| 62  | CML-O | RX8-   | Receiver inverted data output       |

| 63  | CML-O | RX8+   | Receiver non-inverted data output   |

| 64  |       | GND    | Module Ground <sup>Note5</sup>      |

| 65  |       | NC     | No connect                          |

| 66  |       | TBD    | For future use                      |

| 67  |       | VCC    | +3.3V Power Supply                  |

| 68  |       | VCC    | +3.3V Power Supply                  |

| 69  |       | TBD    | For future use                      |

| 70  |       | GND    | Module Ground <sup>Note5</sup>      |

| 71  | CML-I | Tx7+   | Transmitter non-inverted data input |

| 72  | CML-I | Tx7-   | Transmitter inverted data input     |

| 73  |       | GND    | Module Ground <sup>Note5</sup>      |

| 74  | CML-I | Tx5+   | Transmitter non-inverted data input |

| 75  | CML-I | Tx5-   | Transmitter inverted data input     |

| 76  |       | GND    | Module Ground <sup>Note5</sup>      |

# Note:

- 1. Module circuit ground is isolated from module chassis ground within the module.

- 2. Open collector should be pulled up with 4.7K to 10K ohms on host board to a voltage between 3.15V and 3.6V.

Figure 2. Electrical Pin-out Details

#### **ModSell Pin**

The ModSelL is an input pin. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP modules on a single 2-wire interface bus. When the ModSelL is "High", the module will not respond to any 2-wire interface communication from the host. ModSelL has an internal pull-up in the module.

#### **ResetL Pin**

Reset. LPMode\_Reset has an internal pull-up in the module. A low level on the ResetL pin for longer than the minimum pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default state. Module Reset Assert Time (t\_init) starts on the rising edge after the low level on the ResetL pin is released. During the execution of a reset (t\_init) the host shall disregard all status bits until the module indicates a completion of the reset interrupt. The module indicates this by posting an IntL signal with the Data\_Not\_Ready bit negated. Note that on power up (including hot insertion) the module will post this completion of reset interrupt without requiring a reset.

#### **LPMode Pin**

FIBERSTAMP QSFP28 modules operate in the low power mode (less than 1.5 W power consumption). This pin active high will decrease power consumption to less than 1W.

#### **ModPrsL Pin**

ModPrsL is pulled up to Vcc on the host board and grounded in the module. The ModPrsL is asserted "Low" when the module is inserted and deasserted "High" when the module is physically absent from the host connector.

#### IntL Pin

IntL is an output pin. When "Low", it indicates a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt by using the 2-wire serial interface. The IntL pin is an open collector output and must be pulled up to Vcc on the host board.

# **Power Supply Filtering**

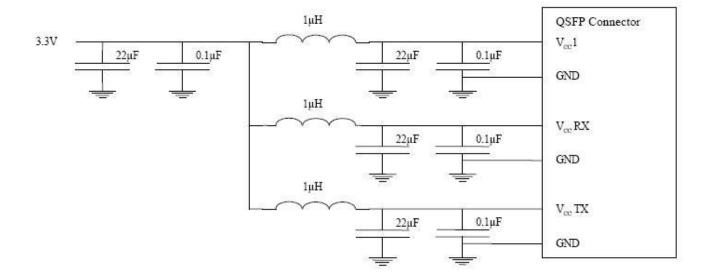

The host board should use the power supply filtering shown in Figure 3.

Figure 3. Host Board Power Supply Filtering

#### DIAGNOSTIC MONITORING INTERFACE

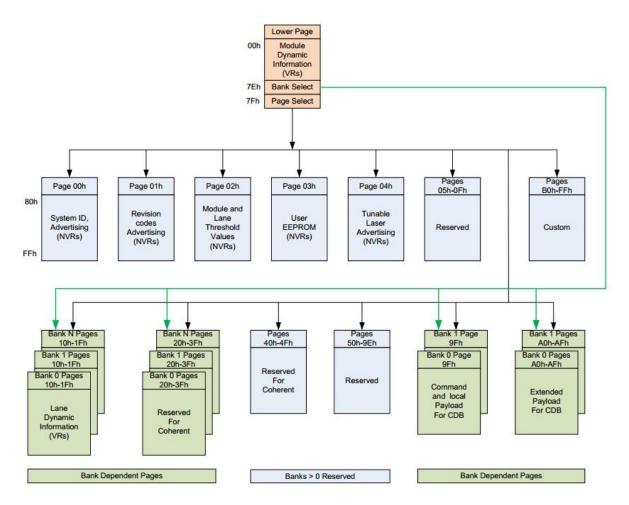

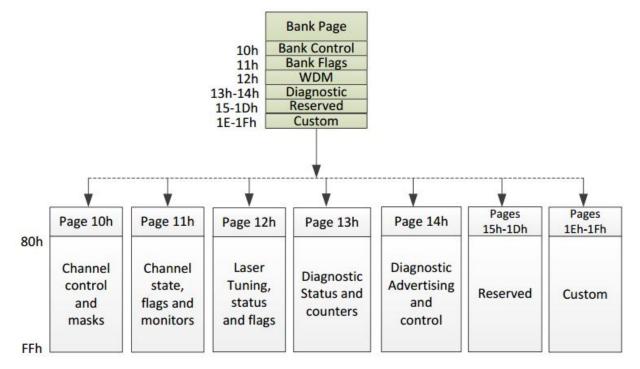

Digital diagnostics functions are available via the I2C interface as specified by CMIS V4.0. The CMIS management memory is shown in **Figure 4**.

Due to eight-bit addresses, the management memory is divided in **Lower Memory** (addresses 00h through 7Fh) and **Upper Memory** (addresses 80h ~ FFh).

The addressing structure of the additional internal management memory is shown in **Figure 5**. The management memory is arranged as a unique and always host accessible address space of 128 bytes (Lower Memory) and as multiple upper address subspaces of 128 bytes each (**Pages**), only one of which is selected as host visible in Upper Memory. A second level of Page selection is possible for Pages for which several instances exist (e.g. where a **bank** of pages with the same Page number exists).

This structure supports a flat 256 byte memory for passive copper modules and permits timely access to addresses in the Lower Memory (e.g. Flags and Monitors). Less time critical entries, e.g. serial ID information and threshold settings, are available with the Page Select function in the Lower Page.

Figure 4. CMIS Bank Page Memory Map

FIBERSTAMP Co,.Ltd.

The CMIS memory structure also provides address expansion by adding additional upper pages as needed. Upper pages 00-02 all contain static, non-volatile advertising registers. Upper page 01 provides revision codes and advertising registers that indicate the capabilities of the module. Upper page 02 provides thresholds for monitored functions. Upper page 03 provides a user read/write space.

The lower page, upper pages 00h-03h and bank 0 page 10h-11h are supported in our module.

Figure 5. Additional Supported Bank Page Memory Map

#### The Lower Memory – Page 00h

The Lower Memory consists of the lower 128 bytes of the 256 byte two-wire serial bus addressable space.

The Lower Page is used to access a variety of module level measurements, diagnostic functions and control functions, as well as to select which of the various Upper Pages in the structured memory map are accessed by byte addresses greater or equal than 128.

| Address | Size | Subject Area              | Description                                                                                                                    |

|---------|------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0–3     | 4    | ID and Status Area        | Module ID from SFF-8024 list, version number, Type and status                                                                  |

|         |      |                           | Flat mem indication, CLEI present indicator, Maximum TWI speed, Current state of Module, Current state of the Interrupt signal |

| 4-7     | 4    | Lane Flag Summary         | Flag summary of all lane flags on pages 10h-1Fh                                                                                |

| 8-13    | 6    | Module-Level Flags        | All flags that are not lane or data path specific                                                                              |

| 14-25   | 12   | Module-Level Monitors     | Monitors that are not lane or data path specific                                                                               |

| 26-30   | 5    | Module Global Controls    | Controls applicable to the module as a whole                                                                                   |

| 31-36   | 6    | Module-Level Flag Masks   | Masking bits for the Module-Level flags                                                                                        |

| 37-38   | 2    | CDB Status Area           | Status of most recent CDB command                                                                                              |

| 39-40   | 2    | Module Firmware Version   | Module Firmware Version.                                                                                                       |

| 41-63   | 23   | Reserved Area             | Reserved for future standardization                                                                                            |

| 64-82   | 19   | Custom Area               | Vendor or module type specific use                                                                                             |

| 83-84   | 2    | Inactive Firmware Version | Version Number of Inactive Firmware. Values of 00h indicates module supports only a single image.                              |

| 85-117  | 33   | Application Advertising   | Combinations of host and media interfaces that are supported by module data path(s)                                            |

| 118-125 | 8    | Password Entry and Change |                                                                                                                                |

| 126     | 1    | Bank Select Byte          | Bank address of currently visible Page                                                                                         |

| 127     | 1    | Page Select Byte          | Page address of currently visible Page                                                                                         |

Figure 6. The Lower Memory Overview

#### The Upper Memory – Page 00h

Upper page 00h contains static read-only module identification information.

| Address | Size<br>(bytes) | Name                               | Description                                               |

|---------|-----------------|------------------------------------|-----------------------------------------------------------|

| 128     | 1               | Identifier                         | Identifier Type of module                                 |

| 129-144 | 16              | Vendor name                        | Vendor name (ASCII)                                       |

| 145-147 | 3               | Vendor OUI                         | Vendor IEEE company ID                                    |

| 148-163 | 16              | Vendor PN                          | Part number provided by vendor (ASCII)                    |

| 164-165 | 2               | Vendor rev                         | Revision level for part number provided by vendor (ASCII) |

| 166-181 | 16              | Vendor SN                          | Vendor Serial Number (ASCII)                              |

| 182-189 | 8               | Date Code                          | Mark Arthur Mark Andrew Mark                              |

| 190-199 | 10              | CLEI code                          | Common Language Equipment Identification code             |

| 200-201 | 2               | Module power characteristics       |                                                           |

| 202     | 1               | Cable assembly length              |                                                           |

| 203     | 1               | Media Connector Type               |                                                           |

| 204-209 | 6               | Copper Cable Attenuation           |                                                           |

| 210-211 | 2               | Cable Assembly Lane<br>Information |                                                           |

| 212     | 1               | Media Interface Technology         |                                                           |

| 213-220 | 8               | Reserved                           |                                                           |

| 221     | 1               | Custom                             |                                                           |

| 222     | 1               | Checksum                           | Includes bytes 128-221                                    |

| 223-255 | 33              | Custom Info NV                     | 10.00                                                     |

Figure 7. Page 00h Memory Overview

# The Upper Memory – Page 01h (Advertising)

Upper page 01h contains advertising fields that define properties that are unique to active modules and cable assemblies.

| Byte    | Size<br>(bytes) | Name                                                        | Description                              |

|---------|-----------------|-------------------------------------------------------------|------------------------------------------|

| 128-131 | 4               | Module Firmware and Hardware revisions                      |                                          |

| 132-137 | 6               | Supported link length                                       | Supported lengths of various fiber media |

| 138-139 | 2               | Nominal Wavelength                                          | 8                                        |

| 140-141 | 2               | Wavelength Tolerance                                        |                                          |

| 142-144 | 3               | Implemented Memory Pages and Durations advertising          |                                          |

| 145-154 | 10              | Module Characteristics advertising                          |                                          |

| 155-156 | 2               | Implemented Controls advertising                            | 8 8                                      |

| 157-158 | 2               | Implemented Flags advertising                               |                                          |

| 159-160 | 2               | Implemented Monitors advertising                            |                                          |

| 161-162 | 2               | Implemented Signal Integrity Controls advertising           |                                          |

| 163-166 | 4               | CDB support advertising                                     |                                          |

| 167-168 | 2               | Additional Durations advertising                            |                                          |

| 169-175 | 7               | Reserved                                                    |                                          |

| 176-190 | 15              | Module Media Lane advertising                               |                                          |

| 191-222 | 32              | Custom                                                      |                                          |

| 223-250 | 28              | Extended Module Host-Media Interface<br>Advertising options |                                          |

| 251-254 | 4               | Reserved                                                    |                                          |

| 255     | 1               | Checksum                                                    | Checksum of bytes 130-254 <sup>1</sup>   |

Figure 8. Page 01h Memory Overview

# The Upper Memory – Page 02h (Module and Lane Thresholds)

Upper Page 02h contains the module-defined thresholds for module-level and lane-specific monitors. The presence of Page 02h is advertised in bit 7 in Page 00h byte 2.

| Byte    | Size<br>(bytes) | Name                                | Description          |

|---------|-----------------|-------------------------------------|----------------------|

| 128-175 | 48              | Module-level monitor thresholds     |                      |

| 176-199 | 24              | Lane-specific monitor<br>thresholds |                      |

| 200-229 | 30              | Reserved                            |                      |

| 230-254 | 25              | Custom                              |                      |

| 255     | 1               | Checksum                            | Covers bytes 128-254 |

Figure 9. Page 02h Memory Overview

#### The Upper Memory – Page 10h (Lane and Data Path Control)

The upper memory map page 10h is a banked page that contains lane dynamic control bytes. The presence of Page 10h is advertised in bit 7 in Page 00h byte 2.

| Byte    | Size<br>(bytes) | Name                     | Description                                                                                     |

|---------|-----------------|--------------------------|-------------------------------------------------------------------------------------------------|

| 128     | 1               | DataPathDeinit           | Data Pathcontrol bits for each lane, controls Data Path<br>State machine                        |

| 129-142 | 14              | Lane-Specific Control    | Fields to control lane attributes independent of the Data<br>Path State machine or control sets |

| 143-177 | 35              | Staged Control Set 0     | Fields to configure the selected Application Code and signal integrity settings                 |

| 178-212 | 35              | Staged Control Set 1     | Fields to configure the selected Application Code and signal integrity settings                 |

| 213-231 | 19              | Lane-Specific Flag Masks |                                                                                                 |

| 232-239 | 8               | Reserved                 |                                                                                                 |

| 240-255 | 16              | Custom                   |                                                                                                 |

Figure 10. Page 02h Memory Overview

#### The Upper Memory – Page 11h (Lane Status)

The upper memory map page 11h is a banked page that contains lane dynamic status bytes. The presence of Page 11h is conditional on the state of bit 7 in Page 00h byte 2. All fields on Page 11h are read-only.

| Byte    | Size<br>(bytes) | Name                                            | Description                                                          |

|---------|-----------------|-------------------------------------------------|----------------------------------------------------------------------|

| 128-131 | 4               | Data Path State indicators                      |                                                                      |

| 132-133 | 2               | Reserved                                        |                                                                      |

| 134-152 | 19              | Lane-specific flags                             |                                                                      |

| 153     | 1               | Reserved                                        |                                                                      |

| 154-201 | 48              | Lane-specific monitors                          |                                                                      |

| 202-205 | 4               | Configuration Error Codes                       | Indicates validity of select Application codes                       |

| 206-234 | 29              | Active Control Set                              |                                                                      |

| 235-239 | 5               | Reserved                                        |                                                                      |

| 240-255 | 16              | Host Electrical to Module<br>Media Lane Mapping | Indicates the mapping of Host Electrical lanes to Module Media lanes |

Figure 11. Page 11h Memory Overview

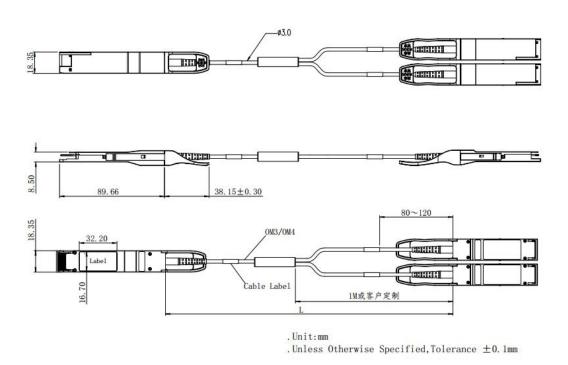

#### **Mechanical Dimensions**

Figure 12. Mechanical Specifications

### **Regulatory Compliance**

FIBERSTAMP FYL2H-400MxxxC 400GbE to 2x200GbE AOC transceiver is Class 1 Laser Products.

They are certified per the following standards:

| Feature          | Agency   | Standard                             |

|------------------|----------|--------------------------------------|

| Laser Eye Safety | FDA/CDRH | CDRH 21 CFR 1040 and Laser Notice 50 |

| EMC              | FCC      | 47 CFR FCC Part 15 Subpart B         |

|                  | CE-EMC   | EN 55032:2015                        |

| EMC              |          | EN 55024:2010+A1:2015                |

| ENIC             |          | EN 61000-3-2:2014                    |

|                  |          | EN 61000-3-3:2013                    |

Complies with FDA performance standards for laser products except for deviations pursuant to Laser Notice No. 50, dated June 24, 2007.

#### **References**

- 1. QSFP DD MAS Rev3.0

- 2. IEEE802.3cd 200GBASE-SR4.

- 3. CMIS V4.0 Management Interface.

- 4. OIF CEI-56G-VSR-PAM4.

Use of controls or adjustment or performance of procedures other than those specified herein may result in hazardous radiation exposure.

#### **Ordering Information**

| Part Number       | Product Description                                              |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| GDA2-MD0401-XXXCA | QSFP56-DD, 400GbE to 2x200GbE MMF Breakout Active Optical Cable. |  |  |

| XXX               | 005-5m, 020-20m, 050-50m, 100-100m                               |  |  |

#### **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by FIBERSTAMP before they become applicable to any particular order or contract. In accordance with the FIBERSTAMP policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of FIBERSTAMP or others. Further details are available from any FIBERSTAMP sales representative.