# 25Gbps 850nm SFP28 SR Optical Transceiver

## FBC-D2585M30T

#### **Features**

- Hot-pluggable SFP28 form factor

- Supports 24.33Gbps and 25.78125Gbps data rate

- Maximum link length of 300m on OM4 MMF with FEC

- 850nm VCSEL laser and PIN photo-detector

- Internal CDR on both Transmitter and Receiver channel

- Duplex LC receptacle

- Single 3.3V power supply

- Power dissipation < 1W</li>

- Digital diagnostics functions are available via the I2C interface

- RoHS-6 compliant

- Case temperature range: -40°C to 85°C

#### **Applications**

- 5G eCPRI SFP28 SR

- 25GBASE-SR SFP28 25G Ethernet

#### **Description**

The FIBERSTAMP Technologies FBC-D2585M30T is a single-Channel, Pluggable, Fiber-Optic SFP28 for 24.33 Gigabit 5G eCPRI SR and 25GBASE-SR SFP28 25G Ethernet Applications. It is a high performance module for short-range data communication and interconnect applications which operate at 24.33 Gbps/25.78125Gbps up to 300m on OM4 fiber. This module is designed to operate over multimode fiber systems using a nominal wavelength of 850nm. The electrical interface uses a 20 contact edge type connector. The optical interface uses duplex LC receptacle. This module incorporates FIBERSTAMP Technologies proven circuit and VCSEL technology to provide reliable long life, high performance, and consistent service.

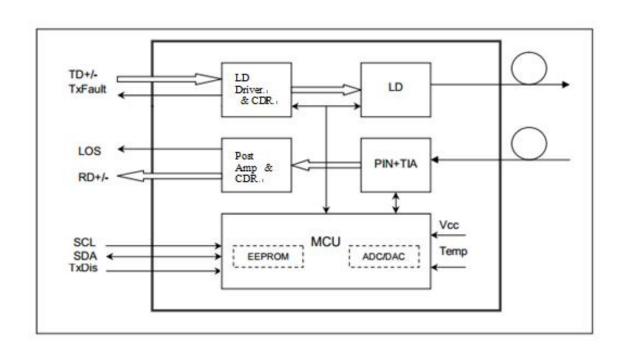

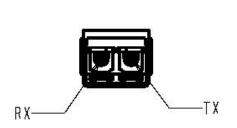

### **Block Diagram**

## **Absolute Maximum Ratings**

## Table 1 - Absolute Maximum Ratings

| Parameter           | Symbol | Min | Max | Unit |

|---------------------|--------|-----|-----|------|

| Supply Voltage      | Vcc    | 0   | 3.6 | V    |

| Storage Temperature | Ts     | -40 | +85 | °C   |

| Operating Humidity  | -      | 5   | 85  | %    |

## **Recommended Operating Conditions**

## Table 2 - Recommended Operating Conditions

| Parameter                                                        | Symbol | Min  | Typical | Max  | Unit |

|------------------------------------------------------------------|--------|------|---------|------|------|

| Operating Case Temperature                                       | Тс     | -40  |         | 85   | °C   |

| Power Supply Voltage                                             | Vcc    | 3.13 | 3.3     | 3.47 | V    |

| Power Supply Current                                             | lcc    |      |         | 300  | mA   |

| Fiber Length on 50/125µm<br>high-bandwidth (OM3) MMF with<br>FEC |        |      |         | 200  | m    |

| Fiber Length on 50/125µm<br>high-bandwidth (OM4) MMF with<br>FEC |        |      |         | 300  | m    |

## Optical and Electrical Characteristics

#### Table 3 - Optical and Electrical Characteristics

| Parameter        |                | Symbol | Min      | Typical | Max      | Unit | Notes |

|------------------|----------------|--------|----------|---------|----------|------|-------|

|                  |                |        | Transmit | ter     |          |      |       |

| Data rate        |                | BR     |          | 24.33   | 25.78125 | Gbps |       |

| Centre Wavele    | ength          | λс     | 840      | 850     | 860      | nm   |       |

| Spectral Width   | (-20dB)        | σ      |          |         | 0.6      | nm   |       |

| Average Outp     | ut Power       | Pavg   | -8.4     |         | 3.4      | dBm  |       |

| Optical Power    | ОМА            | РОМА   | -6.4     |         | 3        | dBm  |       |

| Extinction Ratio | )              | ER     | 2        |         |          | dB   |       |

| Differential dat | ta input swing | VIN,PP | 40       |         | 1000     | mV   |       |

| Input Differenti | ial Impedance  | ZIN    | 90       | 100     | 110      | Ω    |       |

| TV D: 11         | Disable        |        | 2.0      |         | Vcc      | V    |       |

| TX Disable       | Enable         |        | 0        |         | 0.8      | V    |       |

| TV 5             | Fault          |        | 2.0      |         | Vcc      | V    |       |

| TX Fault         | Normal         |        | 0        |         | 0.8      | V    |       |

|                  |                |        | Receive  | er      | 1        |      |       |

| Data rate        |                | BR     |          | 24.33   | 25.78125 | Gbps |       |

| Centre Wavele    | ength          | λς     | 840      | 850     | 860      | nm   |       |

| Stressed Sensiti | ivity (OMA)    |        | -        | -       | -5.2     | dBm  |       |

| Receiver Powe    | er (OMA)       |        |          |         | 3        | dBm  |       |

| LOS De-Assert    |                | LOSD   |          |         | -13      | dBm  |       |

| Parameter                      | Symbol  | Min | Typical | Max | Unit | Notes |

|--------------------------------|---------|-----|---------|-----|------|-------|

| LOS Assert                     | LOSA    | -30 |         |     | dBm  |       |

| LOS Hysteresis                 |         | 0.5 |         |     | dB   |       |

| Differential data output swing | Vout,PP | 300 |         | 850 | mV   |       |

| LOS                            | High    | 2.0 |         | Vcc | V    |       |

|                                | Low     |     |         | 0.8 | ٧    |       |

Notes: Receive Sensitivity measured with a prbs31 pattern @25.78125Gb/s, BER 1E-12;

## **Timing and Electrical**

## Table 4 - Timing and Electrical

| Parameter                                                                                     | Symbol                | Min. | Max. | Unit | Conditions                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------|-----------------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx_Disable assert time                                                                        | t_off                 |      | 100  | μs   | Rising edge of Tx_Disable to fall of output signal<br>below 10% of nominal                                                                                                                                                                                                                                                                      |

| Tx_Disable negate time                                                                        | t_on                  |      | 2    | ms   | Falling edge of Tx_Disable to rise of output signal<br>above 90% of nominal. This only applies in normal<br>operation, not during start up or fault recovery.                                                                                                                                                                                   |

| Time to initialize 2-wire interface                                                           | t_2w_start_up         |      | 300  | ms   | From power on or hot plug after the supply meeting <u>Table 8</u> .                                                                                                                                                                                                                                                                             |

| Time to initialize                                                                            | t_start_up            |      | 300  | ms   | From power supplies meeting <u>Table 8</u> or hot plug or Tx disable negated during power up, or Tx_Fault recovery, until non-cooled power level I part (or non-cooled power level II part already enabled at power level II for Tx_Fault recovery) is fully operational.                                                                       |

| Time to initialize cooled module<br>and time to power up a cooled<br>module to Power Level II | t_start_up_cooled     |      | 90   | 5    | From power supplies meeting <u>Table 8</u> or hot plug, or Tx disable negated during power up or Tx_Fault recovery, until cooled power level I part (or cooled power level II part during fault recovery) is fully operational. Also, from stop bit low-to-high SDA transition enabling Power Level II until cooled module is fully operational |

| Time to Power Up to Level II                                                                  | t_power_level2        |      | 300  | ms   | From stop bit low-to-high SDA transition enabling<br>power level II until non-cooled module is fully<br>operational                                                                                                                                                                                                                             |

| Time to Power Down from Level II                                                              | t_power_down          |      | 300  | ms   | From stop bit low-to-high SDA transition dis-<br>abling power level II until module is within power<br>level I requirements                                                                                                                                                                                                                     |

| Tx_Fault assert                                                                               | Tx_Fault_on           |      | 1    | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                               |

| Tx_Fault assert for cooled module                                                             | Tx_Fault_on_cooled    |      | 50   | ms   | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                                               |

| Tx_Fault Reset                                                                                | t_reset               | 10   |      | μs   | Time Tx_Disable must be held high to reset Tx_Fault                                                                                                                                                                                                                                                                                             |

| RS0, RS1 rate select timing for FC                                                            | t_RS0_FC,<br>t_RS1_FC |      | 500  | μs   | From assertion till stable output                                                                                                                                                                                                                                                                                                               |

| RS0, RS1 rate select timing non FC                                                            | t_RS0, t_RS1          |      | 24   | ms   | From assertion till stable output                                                                                                                                                                                                                                                                                                               |

| Rx_LOS assert delay                                                                           | t_los_on              |      | 100  | μs   | From occurrence of loss of signal to assertion of Rx_LOS                                                                                                                                                                                                                                                                                        |

| Rx_LOS negate delay                                                                           | t_los_off             |      | 100  | μѕ   | From occurrence of presence of signal to negation of Rx_LOS                                                                                                                                                                                                                                                                                     |

## Diagnostics

## Table 5 – Diagnostics Specification

| Parameter    | Range      | Unit | Accuracy | Calibration         |

|--------------|------------|------|----------|---------------------|

| Temperature  | -40 to +85 | °C   | ±3°C     | Internal / External |

| Voltage      | 3.0 to 3.6 | V    | ±3%      | Internal / External |

| Bias Current | 0 to 20    | mA   | ±10%     | Internal / External |

| TX Power     | -8 to 3    | dBm  | ±3dB     | Internal / External |

| RX Power     | -14 to 0   | dBm  | ±3dB     | Internal / External |

## **Digital Diagnostic Memory Map**

| PIN | Logic     | Symbol   | Name / Description                                      | Note |

|-----|-----------|----------|---------------------------------------------------------|------|

| 1   |           | VeeT     | Module Transmitter Ground                               | 1    |

| 2   | LVTTL-O   | TX_Fault | Module Transmitter Fault                                | 2    |

| 3   | LVTTL-I   | TX_Dis   | Transmitter Disable; Turns off transmitter laser output |      |

| 4   | LVTTL-I/O | SDA      | 2-Wire Serial Interface Data Line                       | 2    |

| 5   | LVTTL-I   | SCL      | 2-Wire Serial Interface Clock                           | 2    |

| 6   |           | MOD_AB\$ | Module Definition, Grounded in the module               |      |

| 7   | LVTTL-I   | RSO      | Receiver Rate Select                                    |      |

| 8   | LVTTL-O   | RX_LOS   | Receiver Loss of Signal Indication Active LOW           |      |

| 9   | LVTTL-I   | RS1      | Transmitter Rate Select (not used)                      |      |

| 10  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 11  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 12  | CML-O     | RD-      | Receiver Inverted Data Output                           |      |

| 13  | CML-O     | RD+      | Receiver Data Output                                    |      |

| 14  |           | VeeR     | Module Receiver Ground                                  | 1    |

| 15  |           | VccR     | Module Receiver 3.3 V Supply                            |      |

| 16  |           | VccT     | Module Receiver 3.3 V Supply                            |      |

| 17  |           | VeeT     | Module Transmitter Ground                               | 1    |

| 18  | CML-I     | TD+      | Transmitter Non-Inverted Data Input                     |      |

| 19  | CML-I     | TD-      | Transmitter Inverted Data Input                         |      |

| 20  |           | VeeT     | Module Transmitter Ground                               | 1    |

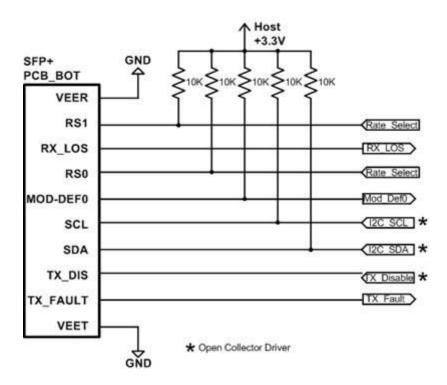

#### Notes:

- 1. Module ground pins GND are isolated from the module case.

- 2. Shall be pulled up with 4.7K-10Kohms to a voltage between 3.15V and 3.45V on the host board

## FIBERSTAMP

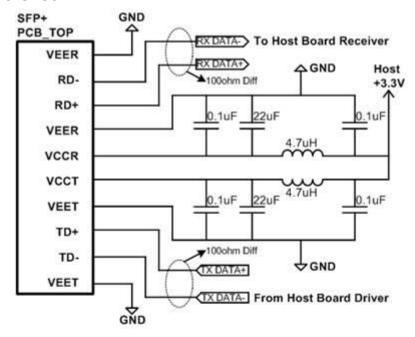

#### **Recommended Interface Circuit**

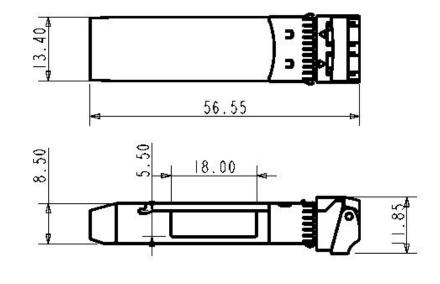

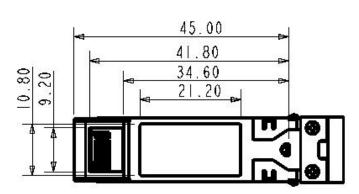

#### **Mechanical Dimensions**

#### **Regulatory Compliance**

FIBERSTAMP FBC-D2585M30T transceivers are Class 1 Laser Products. They are certified per the following standards:

| Feature           | Agency   | Standard                                                                         |

|-------------------|----------|----------------------------------------------------------------------------------|

| Laser Eye Safety  | FDA/CDRH | CDRH 21 CFR 1040 and Laser Notice 50                                             |

| Laser Eye Safety  | TÜ∨      | IEC 60825-1:2014<br>EN 60825-1:2014<br>EN 60825-2:2004+A1+A2                     |

| Electrical Safety | TÜ∨      | EN 60950-1:2006+A11+A12+A2                                                       |

| Electrical Safety | UL/CSA   | UL 60950-1 & CAN/CSA C22.2 No.60950-1<br>CLASS 3862.07<br>CLASS 3862.87          |

| EMC               | FCC      | 47 CFR FCC Part 15 Subpart B                                                     |

| EMC               | CE-EMC   | EN 55032:2015<br>EN 55024:2010+A1:2015<br>EN 61000-3-2:2014<br>EN 61000-3-3:2013 |

Complies with FDA performance standards for laser products except for deviations pursuant to Laser Notice No. 50, dated June 24, 2007.

#### **References**

- 1. SFP MSA

- 2. eCPRI MSA

- 3. Directive 2011/65/EU of the European Parliament and of the Council, "on the restriction of the use of certain hazardous substances in electrical and electronic equipment," July 1, 2011.

Use of controls or adjustment or performance of procedures other than those specified herein may result in hazardous radiation exposure.

#### Ordering Information

| Part Number   | Product Description                                                        |

|---------------|----------------------------------------------------------------------------|

| FBC-D2585M30T | SFP28 SR(Industrial grade), 25.78125/24.33Gb/s, 850nm, 300m on OM4 MMF, LC |

#### **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by FIBERSTAMP before they become applicable to any particular order or contract. In accordance with the FIBERSTAMP policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of FIBERSTAMP or others. Further details are available from any FIBERSTAMP sales representative.